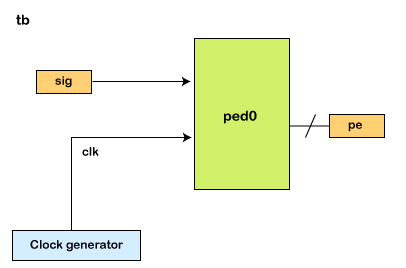

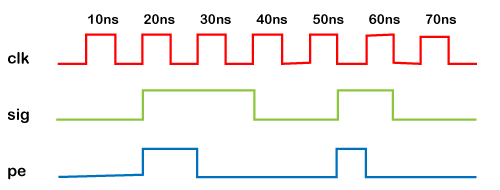

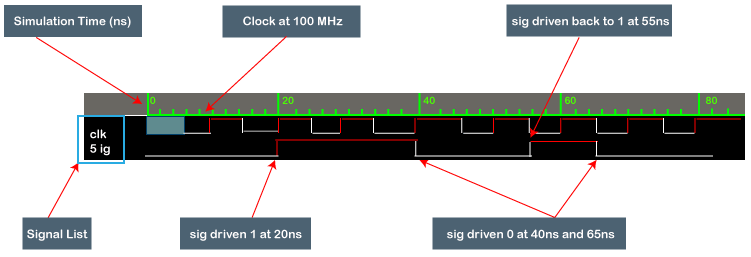

Verilog Simulation BasicsVerilog is a hardware description language, and there is no requirement for designers to simulate their RTL designs for converting them into logic gates.  Simulation is a technique for applying different input stimulus to the design at different times to check if the RTL code behaves in an intended way. Simulation is a well-familiar technique to verify the robustness of the design. It is similar to how a fabricated chip will be used in the real world and how it reacts to different inputs. For example, the above design represents a positive edge detector with inputs clock and signal, which are evaluated at periodic intervals to determine the output. Simulation allows us to view the timing diagram of related signals to understand how the design description behaves in Verilog.  Many EDA companies develop simulators capable of figuring out the outputs for various inputs to the design. Verilog is defined in terms of a discrete event execution model. And different simulators are free to use different algorithms to provide the user with a consistent set of results. The Verilog code is divided into multiple processes and threads and may be evaluated at different times in a simulation. Example In this example, the tb (testbench) is a container to hold a design module. There are two signals or variables that can be assigned individual values at specific times. clk represents a clock which is generated within the testbench. This is done using the always statement by alternating the clock's value after every 5ns. The initial block contains a set of statements that assign different values to both the signals. The simulator provides the following output after execution of the above testbench. Simulation WaveformSimulations allow dumping design and testbench signals into a waveform that can be graphically represented to analyze and debug the RTL design functionality. The waveform shown below is obtained from an EDA tool and shows each signal's progress for time and is the same as the timing diagram.  Every change in the value of a net or variable is called an update event. And processes are sensitive to update events such that these processes are evaluated whenever the update event happens and is called an evaluation event. Because of having the possibility of multiple processes being evaluated arbitrarily, the order of changes has to be tracked in something called an event queue. They are ordered by the simulation time. Placement of a new event in the queue is called scheduling. Simulation time refers to the time value maintained by the simulator to model the actual time it would take for the circuit being simulated.  Regions in an Event queueThe Verilog event queue is divided into five regions, and events can be added to any of them. However, it can be removed only from the active region.

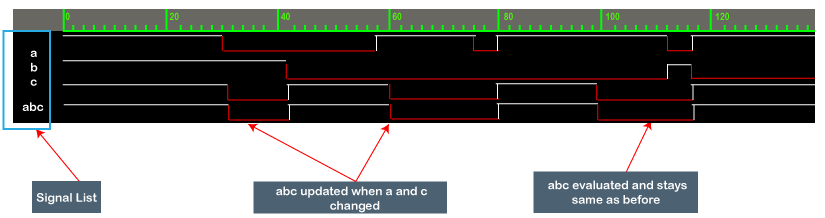

A simulation cycle is where all active events are processed. The standard guarantees a particular scheduling order except for a few cases and. For example, statements inside a begin-end block will only be executed in the order in which they appear. The event queue defines that assignment to b should happen after assignment to a. Next TopicVerilog Timescale |